9

**Research Article**

# Coupling effect in field Hall elements based on thin-film SOI MOS transistors

Aleksey V. Leonov<sup>1</sup>, Victor N. Murashev<sup>2</sup>, Dmitry N. Ivanov<sup>2</sup>, V. D. Kirilov<sup>2</sup>

1 Institute of Microelectronics Technology and High Purity Materials, Russian Academy of Sciences, 6 Academician Ossipyan Str., Chernogolovka, Moscow Region, 142432, Russia

2 National University of Science and Technology MISiS, 4 Leninsky Prospekt, Moscow 119049, Russia

Corresponding author: Dmitry N. Ivanov (ivanovdmitry@rocketmail.com)

Received 16 November 2020 • Accepted 9 December 2020 • Published 30 December 2020

**Citation:** Leonov AV, Murashev VN, Ivanov DN, Kirilov VD (2020) Coupling effect in field Hall elements based on thin-film SOI MOS transistors. Modern Electronic Materials 6(4): 155–158. https://doi.org/10.3897/j.moem.6.4.65567

#### Abstract

The influence of the coupling effect on the parameters of field Hall elements based on thin-film MOS transistors has been studied. Analysis of the development of today's microelectronics shows the necessity of developing the element base for high performance sensors based on silicon technologies. One way to significantly improve the performance of sensing elements including magnetic field sensors is the use of thin-film transistors on the basis of silicon on insulator (SOI) structures. It has been shown that field Hall sensors (FHS) may become the basis of high-performance magnetic field sensors employing the coupling effect occurring in the double gate vertical topology of these sensing elements. Electrophysical studies of FHS have been conducted for different gate bias and power supply modes. The results show that the coupling effect between the gates occurs in FHS if the thickness of the working layer between the gates is 200 nm. This effect leads to an increase in the effective carrier mobility and hence an increase in the magnetic sensitivity of the material. Thus field Hall elements based on thin-film transistors fabricated using silicon technologies provide for a substantial increase in the magnetic sensitivity of the elements and allow their application in highly reliable magnetic field sensors.

### Keywords

transistor, silicon on insulator, field Hall sensor, charge coupling, magnetic field.

## 1. Introduction

Over the last decades microelectronics industry has been developing at a fast pace since it is directly related to the development of information technologies, industrial automation and Internet of things which provide for effective control of human life space. Doubtlessly further achievements of microelectronics will only be possible provided the necessary element base is available, with the emphasis of development being on sensors and microsystems for environmental monitoring [1]. Magnetic field sensors are among the most demanded devices in various general-purpose civil and special applications. It is therefore not surprising that the world's fabrication figures of these sensors amount to billions of devices and grow by about 10% annually [2, 3].

Analysis of publications on sensor technologies shows that silicon is the key material in this segment used for the fabrication of the sensing elements of sensors and the infrastructure electronics for the processing of the signals generated by the sensing elements, as well as for overall sensor operation [4, 5].

A tangible improvement in the performance of silicon microelectronic sensors can be achieved, without abandoning silicon technologies, by fabricating the sensing

© 2020 National University of Science and Technology MISiS. This is an open access article distributed under the terms of the Creative Commons Attribution License (CC-BY 4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

elements from thin-film silicon field effect transistors with two vertical control gates based on silicon on insulator (SOI) structures [6, 7].

Silicon on insulator (SOI) is an important material of silicon macro- and microelectronics. Currently SOI transistors are widely used for the fabrication of various physical, chemical and biological sensors [8–10]. The advantages of SOI structures for sensors fabrication in comparison with conventional bulk substrate technologies mainly include higher element operation temperatures due to lower leakage currents and new functionalities.

SOI MOS field effect transistors typically have two gates. One is for controlling the carrier concentration in the channel and the other at the substrate side is earthed. A distinctive feature of fully depleted SOI MOS transistors is the coupling effect, i.e., a correlation between the interface potentials of the Si thin film in which the device is fabricated and the surrounding dielectric [11–14]. This coupling effect may lead to a dependence of the SOI layer conductivity on the transistor control gate bias and the substrate metallization voltage.

The aim of this work is to study the effect of gate voltage on the Hall voltage in field Hall sensors (FHS) in the form of magnetically sensitive thin-film double gate SOI MOS transistor with probes at two opposite sides of the *n*-Si channel. The SOI FHS operation principle is electron accumulation at the Si–SiO<sub>2</sub> interface boundaries separated by the partial depletion zone.

#### 2. Experimental

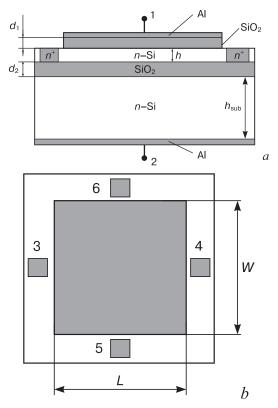

FHS were described in detail earlier [15, 16]. The SOI structures used for FHS fabrication were synthesized by oxygen ion implantation into silicon wafers using the SIMOX technology (Separation by Implantation of Oxygen). The FHS crystal cut from a SOI structure was  $500 \times 500 \times 400 \ \mu m$  in size. The FHS topology in the *n*-conductivity SOI structure silicon layer with an electron concentration of  $5 \cdot 10^{14}$  cm<sup>-3</sup> and 0.2 µm in thickness separated from the substrate by a  $0.35 \,\mu\text{m}$  SiO<sub>2</sub> buried layer. The  $50 \times 50 \,\mu\text{m}$  current and Hall contact pads were produced by phosphorus ion implantation and annealing to a 10<sup>20</sup> cm<sup>-3</sup> concentration in the entire silicon layer depth. Then a 0.35 µm thermal oxide layer was grown on the silicon working layer surface and capped with an Al film. Thus the FHS has a system of two vertical gates for controlling the electrophysical parameters of the device. The FHS design is schematically shown in Fig. 1.

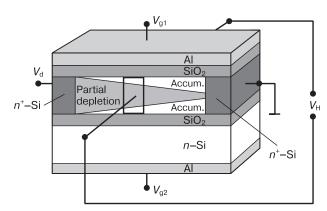

The FHS working principle is electron accumulation at  $\text{Si}-\text{SiO}_2$  interface boundaries and partial Si channel depletion between the electron accumulating zones of the Si film. For further details see Fig. 2 [17].

#### 3. Results and discussion

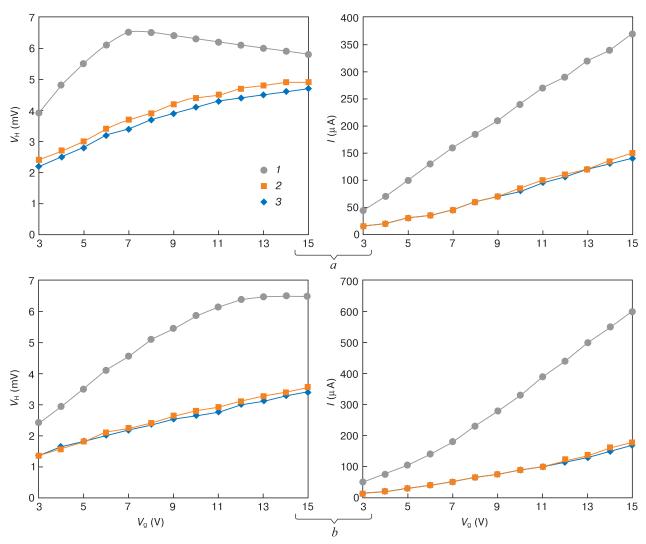

In this work we studied the current and Hall characteristics of the FHS for different gate bias modes: 1) variable bias is applied to each of the gates separately while the other

**Figure 1.** Dimensions and arrangement of SOI FHS elements: (*a*) cross-section and (*b*) top view; (*1* and *2*) top and bottom gate contacts; (*3* and *4*) current (Ohmic) contacts and (5 and 6) side Hall probes.

Parameters:  $h = 0.2 \ \mu\text{m}$  is the working silicon layer thickness,  $d_1 = 0.35 \ \mu\text{m}$  is the top gate dielectric thickness,  $d_2 = 0.35 \ \mu\text{m}$  is the SOI structure buried dielectric layer thickness,  $h_{\text{sub}} = 400 \ \mu\text{m}$ is the substrate thickness,  $L = 500 \ \mu\text{m}$  is the silicon channel length and  $W = 500 \ \mu\text{m}$  is the silicon channel width

**Figure 2.** FHS schematic and working principle explanation:  $V_{d}$  is the FHS power voltage,  $V_{g1}$  and  $V_{g2}$  are the top and bottom FHS gate bias, respectively, and  $V_{H}$  is the Hall voltage read at the Hall probes.

gate has a zero bias and 2) equal bias is applied to both the gates simultaneously. Room temperature experimental curves taken at a 50 mT induction are shown in Fig. 3.

It can be seen from Fig. 3 that applying equal bias  $V_{\rm g}$  to both the gates increases the Hall voltage  $V_{\rm H}$  almost twofold in comparison with single gate bias mode in the

**Figure 3.** Hall voltage and channel current dependences on gate bias  $V_g$  for different gate bias modes and different FHS power voltages  $V_d$  at B = 50 mT: (a):  $V_d = 5$  V; (1)  $V_g = V_{g1}$ ,  $V_{g2} = 0$  V; (2)  $V_g = V_{g2}$ ,  $V_{g1} = 0$  V; (3)  $V_g = V_{g1} = V_g$ ; (b):  $V_d = 10$  V; (1)  $V_g = V_{g1}$ ,  $V_{g2} = 0$  V; (2)  $V_g = V_{g2}$ ,  $V_{g1} = 0$  V; (3)  $V_g = V_{g1} = V_g$ ; (b):  $V_d = 10$  V; (1)  $V_g = V_{g1}$ ,  $V_{g2} = 0$  V; (2)  $V_g = V_{g2}$ ,  $V_{g1} = 0$  V; (3)  $V_g = V_{g1} = 0$  V; (4)  $V_g = V_{g1}$ ,  $V_{g2} = 0$  V; (5)  $V_g = V_{g2}$ ,  $V_{g1} = 0$  V; (7)  $V_g = V_{g1}$ ,  $V_{g2} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g1} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g2} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g1} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g2} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g1} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g2} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g2} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g2} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g2} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g2} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g2} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g2} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g2} = 0$  V; (7)  $V_g = V_{g2}$ ,  $V_{g3} = 0$  V; (7)  $V_g = V_{g3}$ ,  $V_{g3} = 0$  V; (7)  $V_{g3} = 0$  V; (7) V

$V_{\rm g}$  voltage range studied. One can also point out that the FHS channel current *I* increases more than twofold when both the gates are switched on. For the entire gate voltage range studied the ratio of the double gate bias channel current to the single gate bias channel current is twice as large as the ratio of the respective Hall voltages, in accordance with the data summarized in the Table 1. There the notations  $I_{2g}$  and  $I_g$  stand for the channel current for bias  $V_{\rm g}$  applied to both the gates and to one of the gates, respectively. Similarly, the notations  $V_{\rm H2g}$  and  $V_{\rm Hg}$  stand for the Hall voltage for bias  $V_{\rm g}$  applied to both the gates, respectively.

The above regularity can be accounted for by the influence of the coupling effect between the gates of the control field effect transistors of the FHS in double gate bias mode. It was shown [18] that for this type of SOI MOS transistors working in interface electron accumulation mode, the charge centroid may shift to the SOI channel bulk. The bulk carrier mobility is always higher than that at the SiO<sub>2</sub>–Si interface.

**Table 1.** FHS channel current and Hall voltage ratios for different gate bias modes.

| $V_{\rm d}, {\rm V}$ | $V_{g}$ , V | $I_{2g}/I_{g}$ | $V_{\rm H2g}/V_{\rm Hg}$ |

|----------------------|-------------|----------------|--------------------------|

| 5                    | 3           | 3.0            | <u>1.6</u>               |

| 5                    | 5           | 3.3            | 1.8                      |

| 5                    | 7           | 3.6            | 1.7                      |

| 5                    | 9           | 3.0            | 1.4                      |

| 5                    | 12          | 2.8            | 1.4                      |

| 5                    | 15          | 2.6            | 1.3                      |

| 10                   | 3           | 3.3            | 1.7                      |

| 10                   | 5           | 3.5            | 1.7                      |

| 10                   | 7           | 3.9            | 2.0                      |

| 10                   | 9           | 4.0            | 2.0                      |

| 10                   | 12          | 3.9            | 2.0                      |

| 10                   | 15          | 3.8            | 1.9                      |

For a Hall transistor, e.g. an FHS, this may account for the increase in the Hall voltage for double gate bias mode in comparison with single gate bias mode because the contribution of electron scattering at surface states decreases and the effective electron mobility in the channel increases (it is well known that Hall's e.m.f. is proportional to the carrier mobility [19]). The decrease in the Hall signal when the gate bias is higher than the channel power voltage (Fig. 3) is accounted for by the effect of the transverse electric field on the electron mobility [20].

Regarding the channel current one should bear in mind that the FHS contains two parallel-connected Hall type elements (Fig. 2). Hence there are contributions to the channel current both from the increase in the carrier concentration in the electron accumulation layers at the top and bottom  $SiO_2$ -Si interfaces and from the increase in the electron mobility in each of the conducting layers.

#### References

- Huijsing J.H. Smart Sensor System: Why? Where? Now? In: Smart Sensor System. Ed by G.C.M. Meijer. John Wiley & Sons, Ltd, 2008: 1–21. https://doi.org/10.1002/9780470866931.ch1

- Magnetic field sensor market will be worth \$2.9 billion by 2020. URL: https://intelligencecommunitynews.com/magnetic-field-sensor-market-will-be-worth-2-9-billion-by-2020-says-report/

- Magnetic Sensors Market Analysis By Technology. 2016. URL: http://www.grandviewresearch.com/industry-analysis/magnetic-sensors-market

- Baranochnikov M.L. *Mikromagnitoelektronika* [Micromagnetoelectronics]. Vol. 1. Moscow: DMK Press, 2016: 544. (In Russ.)

- Voitovich I.D., Korsunskii V.M. Intellektual 'nye sensory [Intellectual sensors]. M.: Izd-vo Intuit, Binom. Laboratoriya znanii, 2009: 626. (In Russ.)

- Mordkovich V.N. Structures "silicon-on-insulator" a promising material for microelectronics. *Izvestiya Vysshikh Uchebnykh Zavedenii*. *Materialy Elektronnoi Tekhniki = Materials of Electronics Engineering*, 1998; (2): 4–7. (In Russ.)

- Colinge J.-P. Silicon-on-Insulator Technology: Materials to VLSI. Boston: Springer, 2004: 366. https://doi.org/10.1007/978-1-4419-9106-5

- Naumova O.V., Fomin B.I., Safronov L.N., Nasimov D.A., Ilnitskii M.A., Dudchenko N.V., Devyatova S.F., Zhanaev E.D., Popov V.P., Latyshev A.V., Aseev A.L. Silicon nanowire transistors for electron biosensors. *Optoelectron. Instrument. Proc.*, 2009; 54(4): 287–291. https://doi.org/10.3103/S8756699009040013

- Naumova O.V., Fomin B.I., Nasimov D.A., Dudchenko N.V., Devyatova S.F., Zhanaev E.D., Popov V.P., Latyshev A.V., Aseev A.L., Ivanov Yu.D., Archakov A.I. SOI nanowires as sensors for charge detection. *Semocond. Sci. Technol.*, 2010; 25(5): 055004. https://doi. org/10.1088/0268-1242/25/5/055004

- Elfström N., Juhasz R., Sychugov I., Engfeldt T., Karlström A.E., Linnros J. Surface charge sensitivity of silicon nanowires: size dependence. *Nano Lett.*, 2007; 7(9): 2608–2612. https://doi. org/10.1021/nl0709017

#### 4. Conclusion

It was shown that in a field Hall element based on thinfilm SOI MOS transistor working by electron accumulation at  $SiO_2$ -Si interface boundaries, the coupling effect increases the absolute magnetic sensitivity of the device and thus allows fabricating magnetic field sensors based on SOI transistors. These sensors are suitable for operation in high temperature and radiation environments.

- Lim H.K., Fossum J.G. Threshold voltage of thin-film Silicon-on-insulator (SOI) MOSFET's. *IEEE Transactions on Electron Devices*, 1983; 30(10): 1244–1251. https://doi.org/10.1109/T-ED.1983.21282

- Celler G.K. Frontiers of silicon-on-insulator. J. Appl. Phys., 2003; 93(9): 4955. https://doi.org/10.1063/1.1558223

- Rudenko T., Nazarov A., Kilchytska V., Flandre D., Popov V., Ilnitsky M., Lysenko V. Revision of interface coupling in ultra-thin body silicon-on-insulator MOSFETs. *Semicond. Physics, Quant. Electron & Optoelectron.*, 2013; 16(3): 300–309. https://doi. org/10.15407/spqeo16.03.300

- Popov V.P., Ilnitsky M.A., Naumova O.V., Nazarov A.N. Quantum corrections to threshold voltages for fully depleted SOI transistors with two independent gates. *Semiconductors*, 2014; 48(10): 1312– 1317. https://doi.org/10.1134/S1063782614100248

- Mordkovich V.N., Baranochnikov M.L., Leonov A.V., Mokrushin A.D., Omelianovskaya N.M., Pazhin D.M. Field Hall device – a new type of magnetic field transducer. *Datchiki i sistemy = Sensors and Systems*, 2003; (7): 33–38. (In Russ.)

- 16. Mokrushin A.D., Omelyanovskaya N.M., Leonov A.V., Mordkovich V.N., Pazhin D.M. Radiation effects in SOI magnetosensitive elements under different irradiation conditions. In: *Scientific and technical collection. Radiation resistance of electronic systems "Resistance-2000"*. Moscow: SPELS, 2000; 3: 38–42. (In Russ.)

- Leonov A.V., Malykh A.A., Mordkovich V.N., Pavlyuk M.I. Multichannel and multifunctional frequency-output sensors of physical effects based on a universal field transistor-type sensing element with a silicon-on-insulator structure. *Instrum. Exp. Tech.*, 2018; 61(2): 299–305. https://doi.org/10.1134/S002044121801027X

- Naumova O.V., Zaitseva E.G., Fomin B.I., Ilnitsky M.A., Popov V.P. Density dependence of electron mobility in the accumulation mode for fully depleted SOI films. *Semiconductors*, 2015; 49(10): 1316–1322. https://doi.org/10.1134/S1063782615100176

- Popovich R.S. Hall Effect Devices. Bristol (Philadelphia): IOP Publishing Ltd, 2004: 419.

- Sze S.M. Physics of Semiconductor Devices. Wiley-Interscience, 1981: 880.